Проведённое исследование растактовки цикла чтения ДВК-1 позволяет более объективно оценить число тактов, необходимых процессору 1801ВМ1 для выполнения различных команд.

CPU:

ROM:Скрытый текст

[свернуть]

DEV:Скрытый текст

[свернуть]

RAM:Скрытый текст

[свернуть]

Скрытый текст

[свернуть]

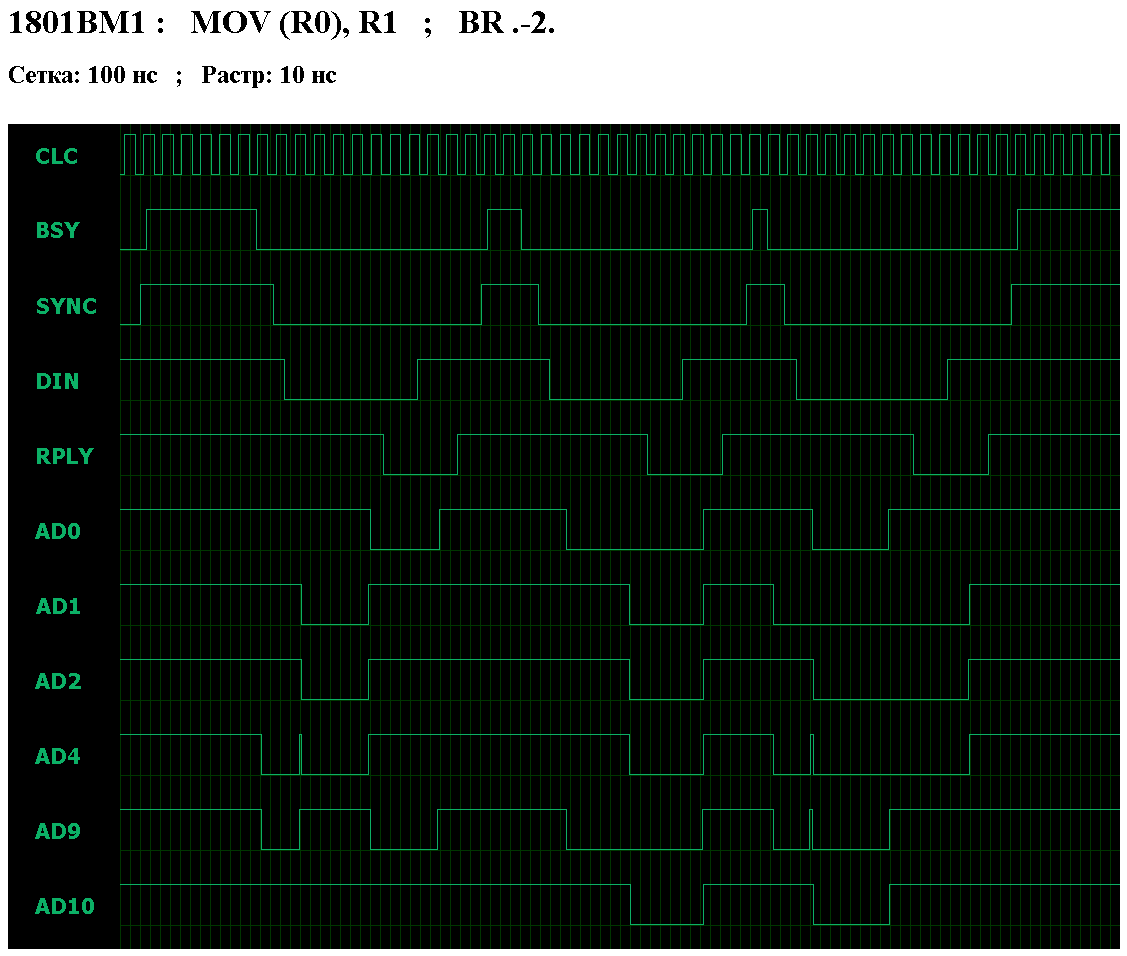

MOV (R0), R1

BR .-2.

Скрытый текст

[свернуть]

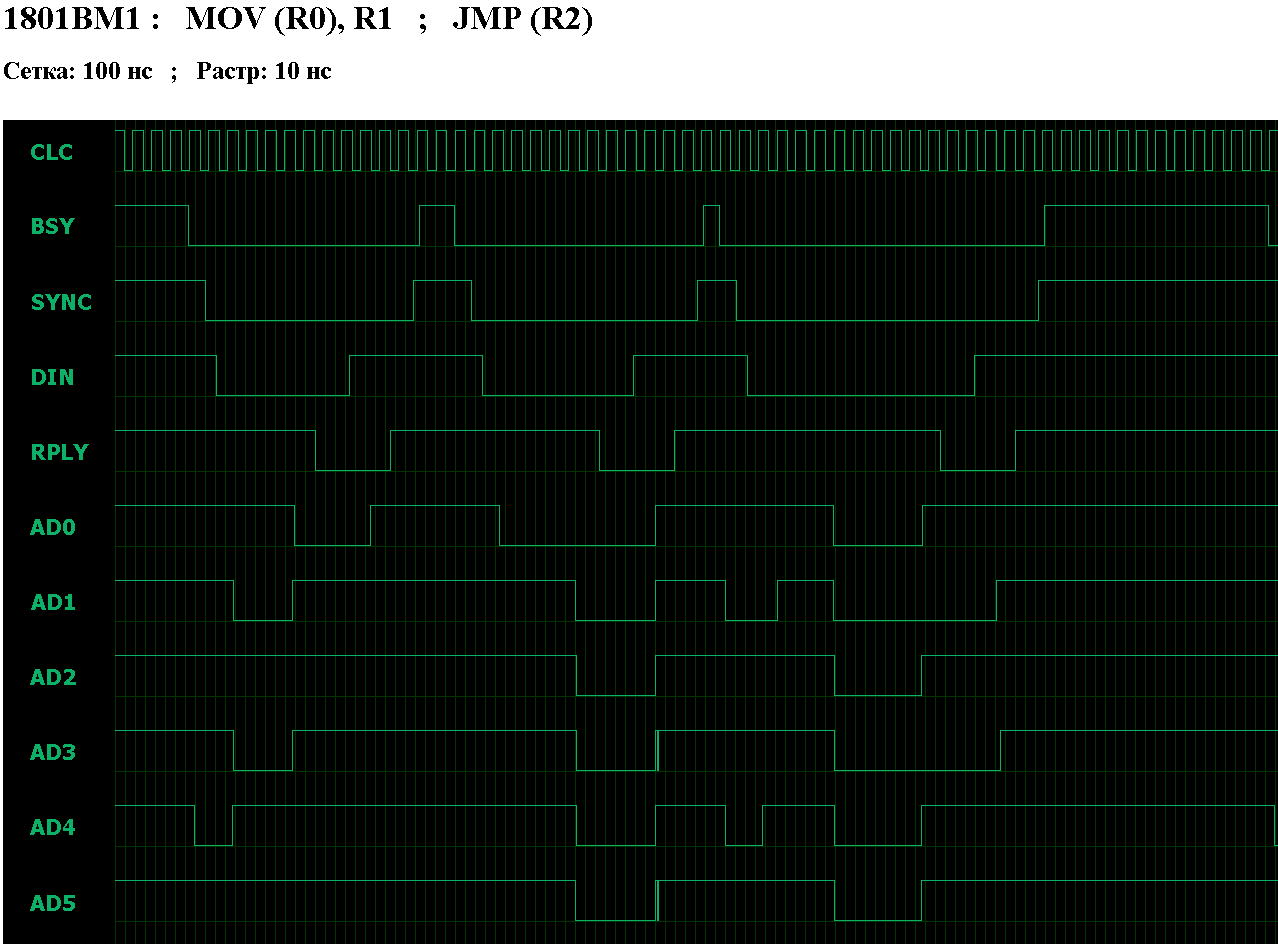

MOV (R0), R1

JMP (R2)

Скрытый текст

[свернуть]

Для первых 4-х наблюдений можно составить следующую таблицу зависимости продолжительности выполнения команды в тактах ( интервал BSY1-BSY1 ) от продолжительности DIN1-RPLY1:

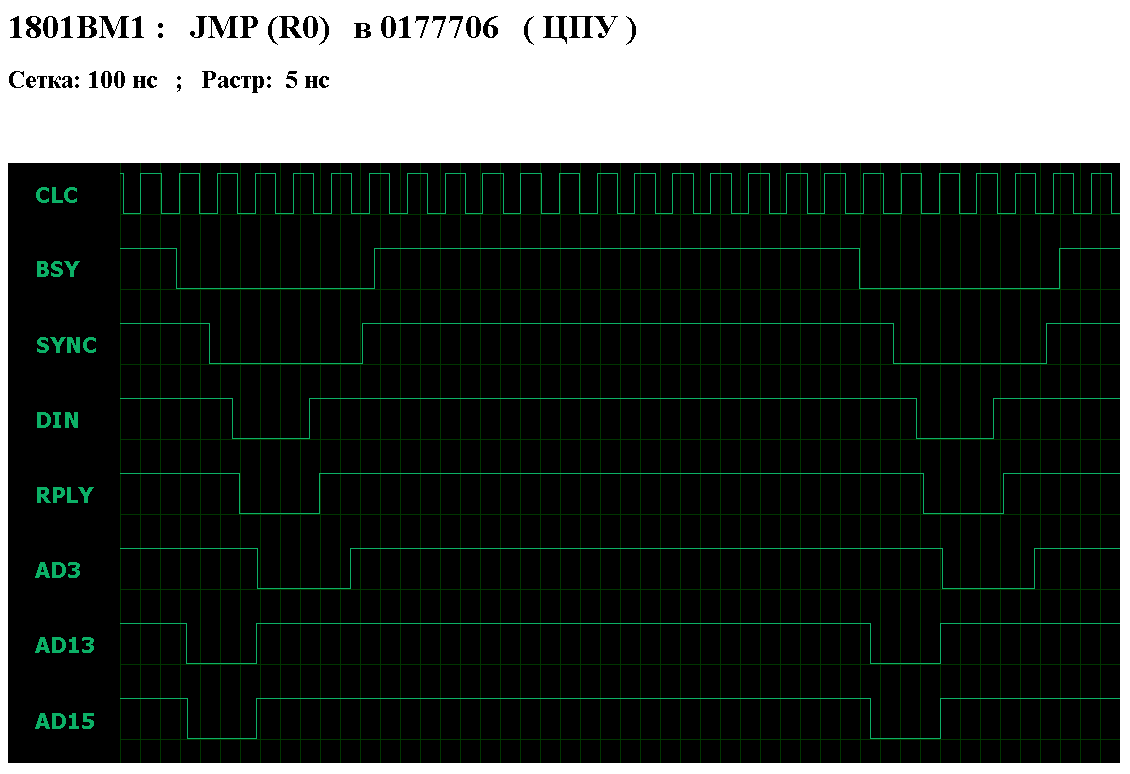

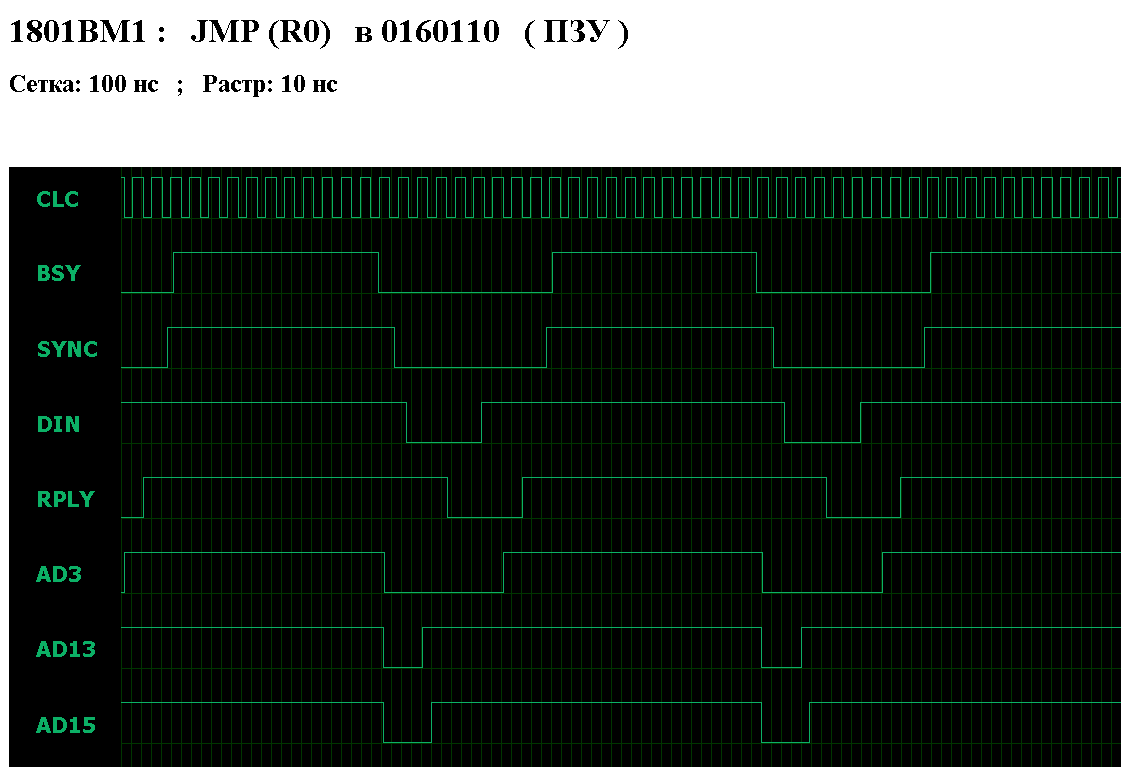

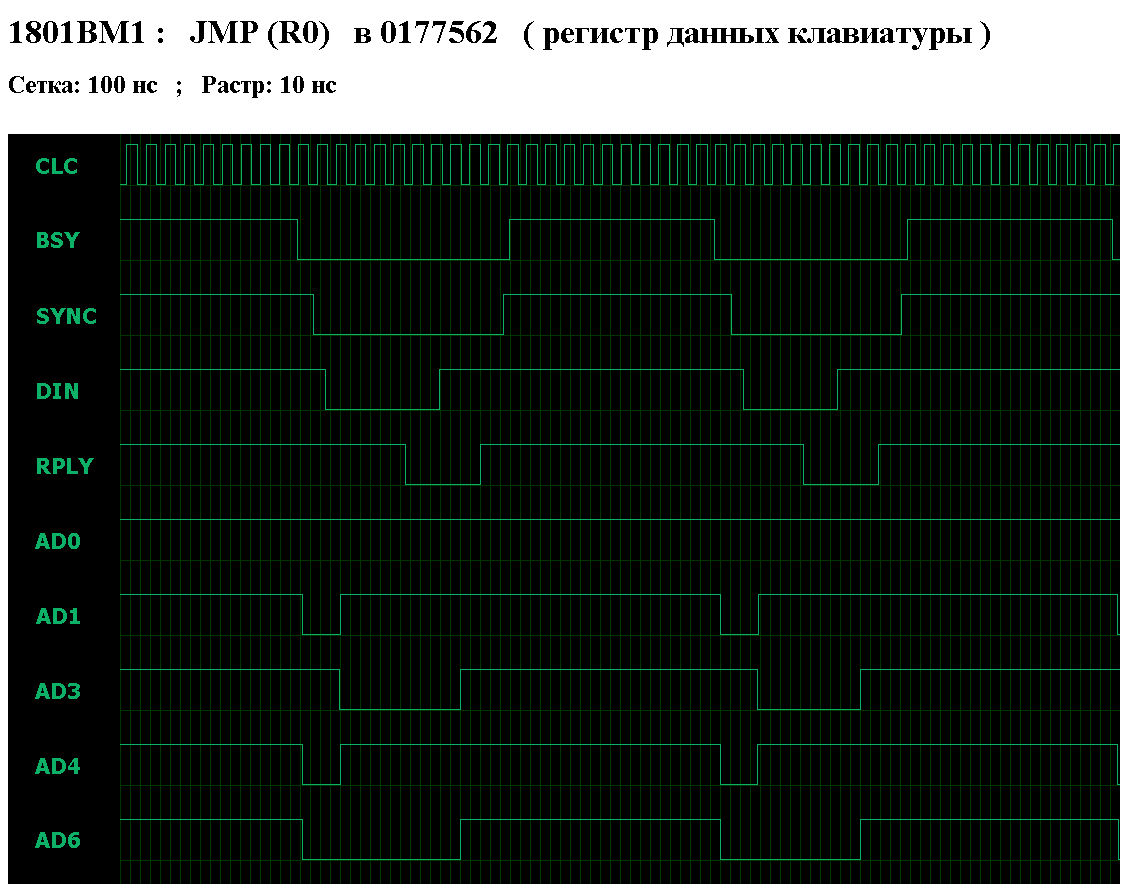

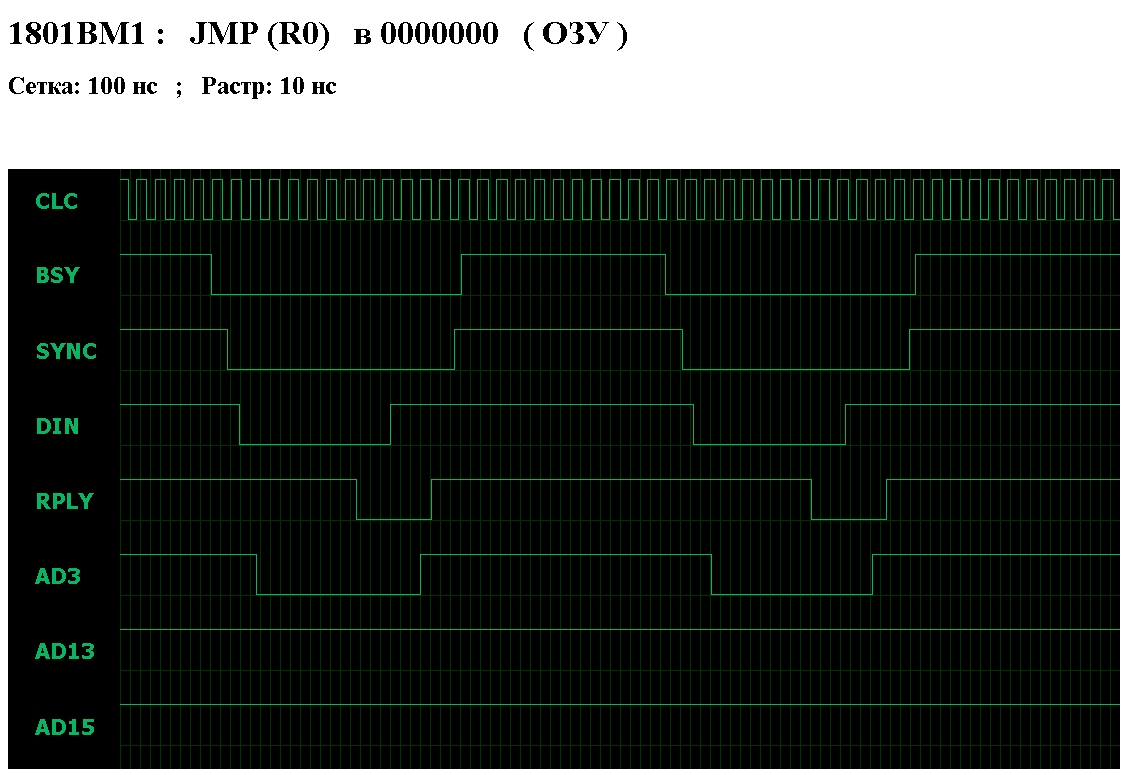

Основные выводы следующие:Код:JMP (R0) в 0177706 ( CPU ): DIN1-RPLY1 == 0 ; BSY1-BSY1 == 18 JMP (R0) в 0160110 ( ROM ): DIN1-RPLY1 == 2 ; BSY1-BSY1 == 20 JMP (R0) в 0177562 ( DEV ): DIN1-RPLY1 == 4 ; BSY1-BSY1 == 22 JMP (R0) в 0000000 ( RAM ): DIN1-RPLY1 == 6 ; BSY1-BSY1 == 24

1. Растактовки цикла чтения ( цикл DATI ) имеют только один интервал, зависящий от типа адресуемой памяти - это интервал между установкой DIN и установкой RPLY ( DIN1-RPLY1 ).

2. Обработка процессором принятых данных начинается сразу после снятия сигнала DIN ( событие DIN0 ), поэтому время выполнения команд не зависит от продолжительности интервала DIN0-RPLY0.

3. Число дополнительных к интервалу DIN1-RPLY1 тактов, необходимых для выполнения команды - неизменно.

Ответить с цитированием

Ответить с цитированием