shit emulator ������ ... /joking ... let me review it...

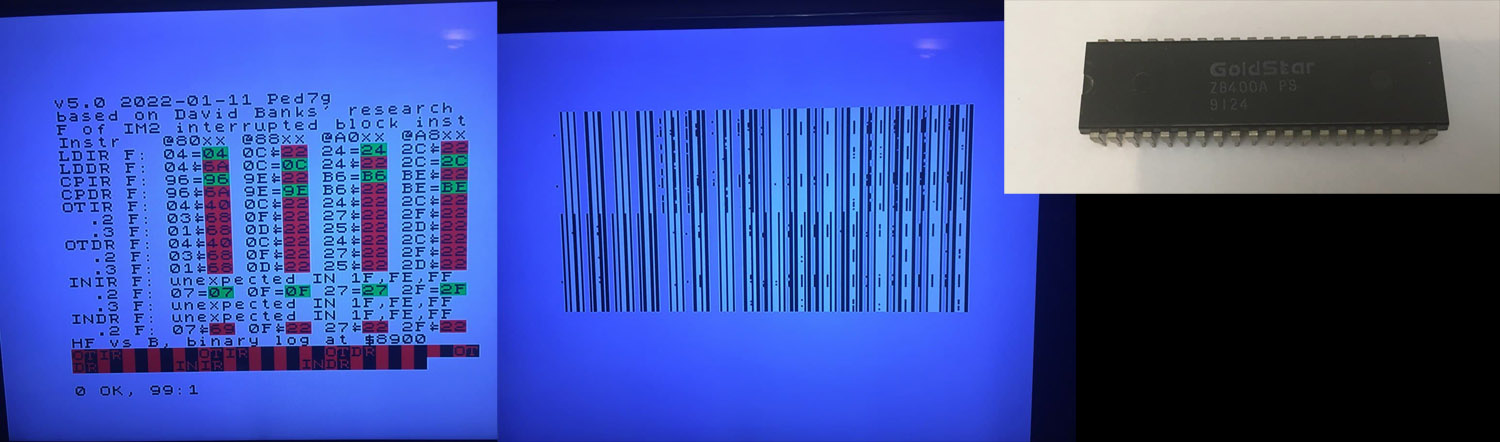

the first photo, first LDIR ... 0c!=22 ... that's PV=0, that's "impossible" during LDIR ... so that's either not real Z80 CPU, or the interrupt did happen after LDIR was finished already, ie. skipping interrupts?? or something else... interrupt too soon before LDIR? Either it's some timing instability (/INT not hitting LDIR) or random bursts of turbo causing the delay to ends sooner/later than expected and INT is stable.

trying to understand rest of the results is then probably meaningless, as that test is not working as it should, for who knows why.

"impossible" -> as long as we agree that ldir works in first four cycles as ldi and then the "r" fifth cycle decides if the PC is reverted based on PV (BC!=0).

the bottom red line with OTIR .. wait, how is that printed this way... shouldn't they be next to each other? the rst $10 works differently in this ROM?? hm...

yep.. that's completely something weird... must be some ROM doing something else on rst $10 ... anyway, that shouldn't affect the F values, so that's just visual weirdness. But that machine will hardly qualify as ZX48 or ZX128 ... ������

the other photos... still LDIR/LDDR have for example several 6A fails, with missing PV=1, so either not interrupted during LDIR, or the LDIR implementation in CPU is completely different from Z80.

so I wouldn't worry about the other values, if the test can't even interrupt the correct instruction, it's pretty pointless to judge those results.

the test does one delay-calibration-round before testing, if the calibration delay is too short (7MHz), the test will error out. So it's rather about the machine being unstable, not having same period or CPU speed than during the test (vs calibration)

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию